About me

I am a PhD candidate at the Center for Cybersecurity, New York University (NYU), advised by Prof. Brandon Reagen. I’m broadly interested in cryptographically secure privacy-preserving machine learning (PPML) and work at the intersection of deep learning and applied cryptography (homomorphic encryption and multiparty computation) as a part of DPRIVE projects. My primary research focuses on the design and optimization of neural networks for efficient processing of encrypted inputs in Private Inference.

In the first half of my PhD, I worked on nonlinear-efficient CNNs and developed ReLU-optimization techniques (DeepReDuce, ICML'21), and proposed methods for redesigning existing CNNs (DeepReShape, TMLR'24) for end-to-end private inference efficiency. Currently, I’m working on the privacy and security of the large language model (LLM).

In addition to my research, I’ve also served as a (invited) reviewer for NeurIPS'23, ICLR'24, CVPR'24, and ICML'24. If you think we could benefit from working together, don’t hesitate to email me!

- Machine Learning Privacy and Security

- Privacy-preserving Computation

- Applied Cryptography

Ph.D. in Privacy-preserving Deep Learning, 2020 - present

New York University

M.Tech. (Research Assistant) in Computer Science and Engineering, 2017 - 2020

Indian Institute of Technology Hyderabad

B.Tech. in Electronics and Communication Engineering, 2009 - 2013

National Institute of Technology Surat

Featured Publications

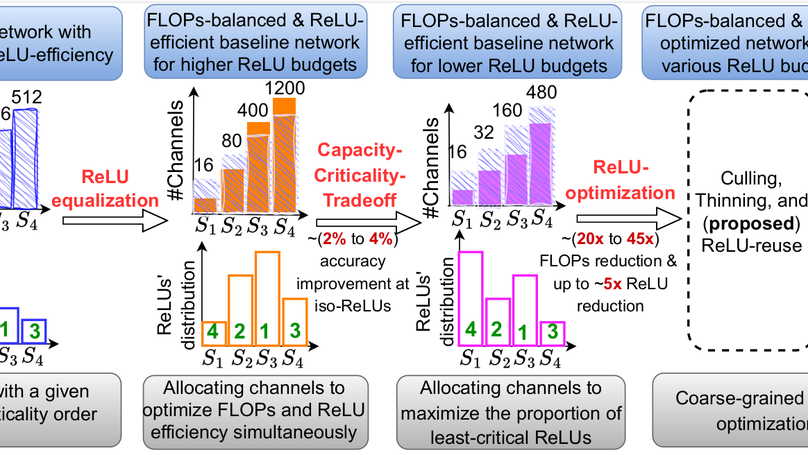

DeepReShape is the first work to conduct a rigorous characterization of desirable neural network attributes for efficient Private Inference (PI). We discovered that distinct network attributes are required for different ReLU counts; in particular, wider networks are beneficial only for higher ReLU counts, whereas networks with a greater proportion of least-critical ReLU are desirable for lower ReLU counts. Further, we introduced a novel network design principle called “ReLU-equalization” to strategically allocate channels within the network to optimize ReLUs and FLOPs efficiency simultaneously. DeepReShape outperforms the current SOTA (SENets, ICLR'23) by achieving a 2.1% increase in accuracy and a 5.2x faster runtime at iso-ReLU counts on CIFAR-100, and an 8.7x faster runtime at iso-accuracy on the TinyImageNet dataset.

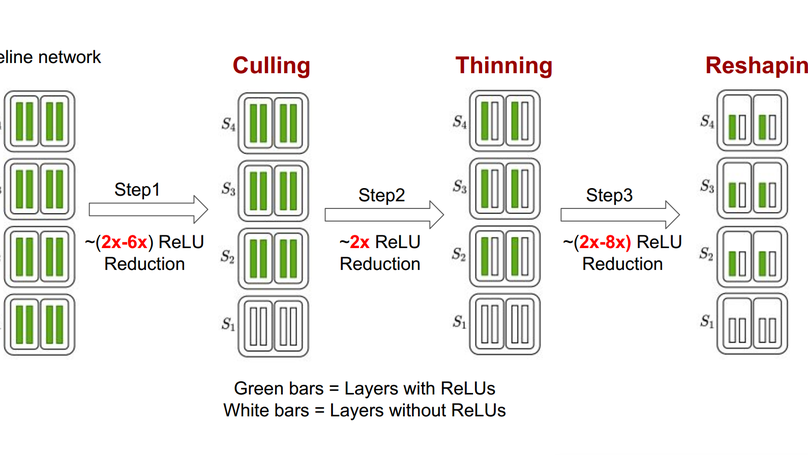

DeepReDuce is a set of optimizations for the judicious removal of ReLUs to reduce private inference latency by leveraging the ReLUs heterogeneity in classical networks. DeepReDuce strategically drops ReLUs upto 4.9x (on CIFAR-100) and 5.7x (on TinyImageNet) for ResNet18 with no loss in accuracy. Compared to the state-of-the-art for private inference DeepReDuce improves accuracy and reduces ReLU count by up to 3.5% (iso-ReLU) and 3.5×(iso-accuracy), respectively.

Recent Publications

Experience

Responsibilities include:

- Designing power delivery circuit for M.2 Solid State Drives.

- Electrical characterization of DRAM and NAND modules

- Signal Intergrity verification of DRAM/NAND datapath

Contact

- nj2049@nyu.edu

- +1 929 513 1083

- 1032-3, 10th floor, 370 jay street, Brooklyn, NY 11201

- Book an appointment

- DM Me